# An Audio Regulator Dynamic Tester Preview

### Walt Jung

This brief note focuses on an audio regulator dynamic test method, which applies a pulse load to a working Super Regulator (SR) It allows examining the resulting transient error across the output. This is especially useful towards determining dynamic stability for various degrees of capacitive loading. Or, to determine regulation impedance.

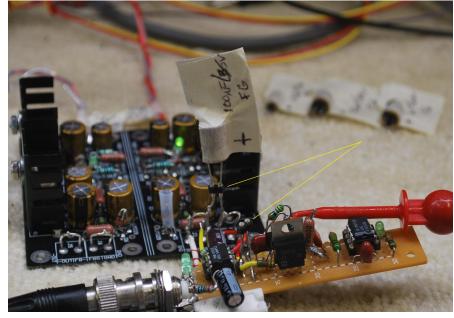

*Figure 1* is a working setup. Under test here is a "SR2020" positive regulator, similar in many regards to the *Audio-Electronics* issue 4/2000 "SR" circuit. [1] In the present case it is vintage 2020, thus SR2020.

### Figure 1: A Dynamic Regulator Test

The external DC load on this (+) 13.7V test regulator is ~60mA. Dynamic AC loading of the tester is ~100mA (peak). The tester circuit is on the breadboard foreground.

Note that the tester is hard soldered to the Vout Force/Sense terminals, using #18 short solid wires. AC sensing is done via the  $100\Omega$  resistor and the flexible red wire to Vout Force/Sense. The dynamic tester load current is returned to Vout Force/Sense nodes via smaller enamel wires.

Test capacitors are plugged into the Vout node 0.1" female pins, or similar pins on the tester (yellow arrows mark these sockets). This provides contrast between local/remote loads. Electrically, this is in parallel to C4 on the regulator PCB. The test cap is denoted as "C4R".

### Table 1: C4R Capacitor Types Tested

| C4R                    | Vendor          | Series          | Catalog #              |

|------------------------|-----------------|-----------------|------------------------|

|                        |                 |                 |                        |

| 10uF/50V               | Nichicon        | FG              | UFG1H100MDM            |

| 22uF/63V               | Nichicon        | FG              | UFG1J220MPM            |

| 33uF/63V               | Nichicon        | FG              | UFG1J330MPM            |

| <mark>100uF/35V</mark> | <b>Nichicon</b> | <mark>FG</mark> | UFG1V101MPM            |

| 100uF/25V              | Nichicon        | KZ              | UKZ1E101MPM            |

| 100uF/25V (not tested) | Panasonic       | FC              | EEU-FC1E101SB          |

| 120uF/25V (tested)     | Panasonic       | FC              | EEU-FC1E121 (obsolete) |

| 100uF/25V              | Nichicon        | PJ              | UPJ1E101MED            |

An Audio Regulator Dynamic Tester Preview Walt Jung <SR2020@waltjung.org> 1/31/2021 Second of five articles within the SR2020 Project Page - 1 -

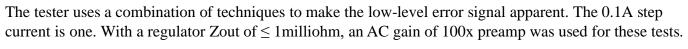

### Figure 2: The Array of Caps Tested

The array of electrolytic caps tested are shown in the top row of the picture at the left. They correspond to those listed as C4R within *Table 1*.

The prototype tester is shown in the foreground, disconnected from the regulator.

A pair of high-Q film caps are also shown for reference, in the middle. Either of these cap types, stacked film or box style, could (and did) introduce in-stability. They are shown here only to emphasize the point that they should not be used!

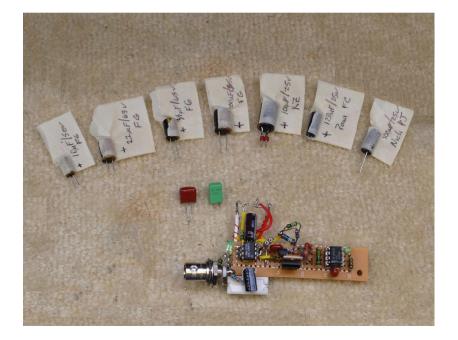

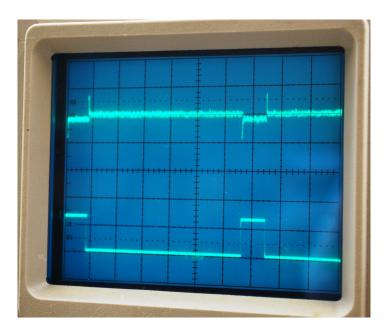

### Figure 3: Dynamic Test Waveforms

Within the as-tested circuit board assembly, the electrolytics used are all from the Nichicon FG series: 22uF/63V (1) at Vraw input, and 100uF/35V elsewhere (3). Here a 100uF/35V cap is under test at C4R (as yellow-highlighted in *Table 1*). Note that the PCB C4 is removed for these tests.

#### Upper Trace:

The Vout AC waveform Verr. as seen directly at the +/- sense points. The vertical scale is 10mV / major division, and after the tester preamp 100x AC gain, the effective scope display is  $100\mu V / div$ .

#### Lower Trace:

SR2020 regulator drive. Positive peak corresponds to 100mA AC load.

#### **Discussion:**

*Figure 3* above shows the error voltage of the test regulator in the upper trace, with a step load change of

100mA (lower trace). The pulse risetime is controlled at ~10 $\mu$ s, consistent with audio bandwidths. Artifacts are the residual wideband baseline noise, mostly the AD825 op amp input noise. There are also narrow transient switching spikes. The spikes appear in all the readings taken, but are considered benign, as real audio signals likely won't have 10 $\mu$ s risetimes. See more on this under the **Spikes:** section.

Interestingly, with all the capacitors shown in the upper row of *Fig. 2*, the *Vout AC error voltage waveform varied little*. Thus, it is considered pointless to show all of them here. This factor suggests that the transient errors displayed are not a strong function of the capacitor type, so much as it is of the intrinsic regulator impedance. This makes intuitive sense, as the tested capacitors generally have an ESR of 100 or more times the regulator Zout.

The P-P regulator error voltage Verr is barely perceptible on the  $100\mu$ V/ major division scale of *Fig. 3*, where the minor divisions correspond to  $20\mu$ V. The stepped portion is of primary interest, and it is roughly a trace width, i.e., ~20  $\mu$ V or so. Since Zout can be computed as Verr/I, this would correspond to an impedance of ~0.0002  $\Omega$  (or ~200  $\mu$ \Omega).

Allowing for various uncertainties, this is roughly consistent with the expected error voltage for a 0.1A load step and an AD825-based regulator. If we assume a regulator open loop Zout of 1 $\Omega$  and an op amp open loop gain of 6500 (76dB), the expected closed loop Zout should be around 1/6500, or 154  $\mu\Omega$ . While this is in the correct ballpark, one should also say this is not a precise measurement.

An important feature of the observed error voltage is that it is flat, with no overshoot or ringing. Various other electrolytics were tested by insertion into the PCB test jack, and to simplify, *none of them caused any serious aberrations* — *no overshoots, and no ringing*. No instability was noted, suggesting that the exact type of electrolytic is not extremely critical. As a guideline, the 100uF/25V Nichicon KZ and 100uF/35V Nichicon FG types have a typical 100kHz ESR between 150 and 200m $\Omega$ . Either of these families can be recommended.

Past capacitor tests have noted that 100-120uF types with 25V (or more) voltage ratings are suitable for these regulator circuits. [2] Bear with us on this — the summaries of this old letter seem on point, even after many years. It should not be necessary to repeat the above dynamic load tests with other (modern) electrolytics, so long as they fall within a window for ESR.

We suggest a threshold of caution here, namely a 100kHz ESR of not less than 100 m $\Omega$ . In the other way, higher ESR is generally OK, so long as it does not exceed about an ohm. For example, a more general-purpose Nichicon 100uF/25Vfrom the UPJ series [3] was also tested in one PCB build (four locations) and worked well. This unit has a 100kHz ESR of 0.39 $\Omega$ . A summary of the electrolytic cap types used at test location C4R is shown in *Table 1*. This not an all-inclusive list, by any means.

### Spikes:

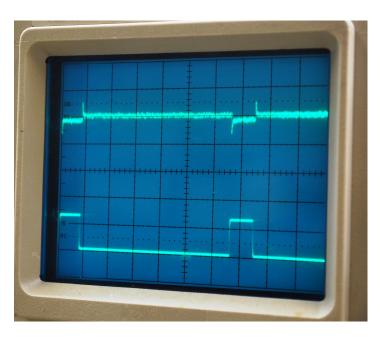

Looking into the narrow spikes as shown in *Fig. 3*, these are related to the risetime of the test signal used. The error voltage for this rise/fall period has a greater rate of change, and the regulator produces a higher amplitude, narrow spike to track the signal slope. *Figure 4* opposite shows the error voltage (upper trace) of a second test regulator, again with a step load change of 100mA (lower trace). As in *Fig. 3*, the pulse risetime is controlled at ~10 $\mu$ s. This is test condition (*A*). Here the amplitude of the narrow spikes can be seen to be ~80 $\mu$ V. Within the tester, the capacitor controlling rise and fall times is 1nF (same conditions as in the *Fig. 1* tests). The lower frequency rectangular portion of this waveform is like *Fig. 3*.

*Figure 5* shows the error voltage (upper trace) of the same regulator with a step load change of 100mA. The pulse risetime is now  $\sim 20\mu$ s., double that of condition (*A*). This is test condition (*B*), and the amplitude of the spikes reduce to  $\sim 40\mu$ V, indicating the regulator is better able to track the slower signal.

## Figure 4: Test Waveform Spikes (A)

A second assembled SR2020 PCB was also tested, to explore the spikes. In this setup, the electrolytics used are all from Nichicon FG and KZ series: A 22uF/63V FG (1) at Vraw input, and 100uF/25V KZ types elsewhere (4). This test (*A*) was otherwise like the *Fig. 1* conditions.

#### Upper Trace:

The Vout AC waveform Verr. with tester preamp 100x AC gain, and effective scope display of  $100\mu$ V / div. Note spike amplitude of ~ $80\mu$ V.

Lower Trace:

SR2020 regulator drive, 100mA AC load. *Note relatively fast risetime*.

# Figure 5: Test Waveform Spikes (B)

In this same SR2020 PCB, a second test (*B*) was performed with the risetime capacitance doubled. This test was otherwise like the *Fig. 4* conditions.

#### Upper Trace:

The Vout AC waveform Verr. with tester preamp 100x AC gain, and effective scope display of  $100\mu$ V / div. Note lower spike amplitude of ~ $40\mu$ V.

Lower Trace:

SR2020 regulator drive, 100mA AC load. Note relatively slow risetime.

#### **Caveats:**

This tester involves very low-level signals, and it requires incredibly careful construction to provide meaning. Thus, it is *not* a project for the inexperienced. This present writeup is a preview of a longer work, which will hopefully contain more details.

#### **References:**

[1] https://refsnregs.waltjung.org/Improved\_PN\_Regs.pdf

- [2] https://refsnregs.waltjung.org/CAP\_LTEs\_060620.pdf

- [3] https://www.mouser.com/ /?Keyword=UPJ1E101MED&bws=1